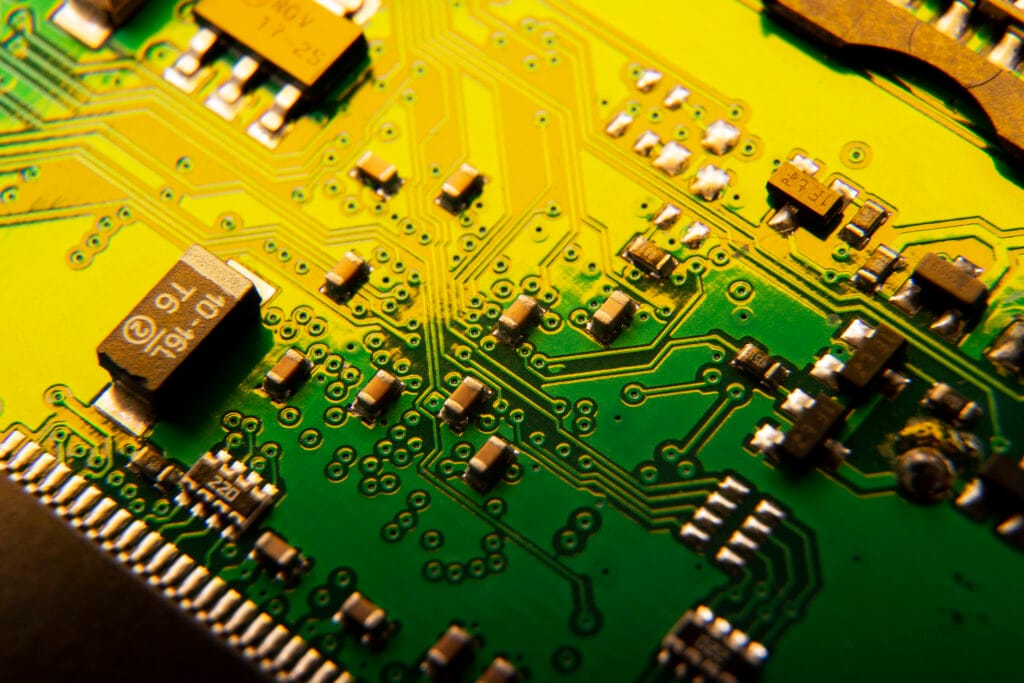

Power efficiency is a critical factor when working with Field Programmable Gate Arrays (FPGAs).

Whether the application is a compact embedded system or a large data center deployment, managing power effectively can reduce heat generation, improve reliability, and lower operational costs.

This blog explores proven techniques that engineers and developers can implement to optimize power consumption in FPGA-based designs.

Understanding FPGA Power Consumption

Before applying any strategy, it is essential to understand where power is consumed. FPGA power usage is generally divided into two categories: static power and dynamic power.

Static power is the energy consumed when the FPGA is powered on but not actively switching logic.

Dynamic power is generated when signals toggle during operation.

Both components must be addressed to achieve true power efficiency.

Choose the Right FPGA Device

Selecting an FPGA that aligns with the project requirements is the first step.

Modern FPGA families from vendors like Xilinx and Intel offer low-power variants designed for applications such as portable electronics, edge computing, and industrial IoT.

Evaluating process technology, available resources, and the operating voltage helps ensure you are not over-provisioning for your workload.

Optimize Clock Management

Clock networks are significant contributors to dynamic power. Using techniques like clock gating can reduce unnecessary toggling.

Adjusting clock frequencies to match performance needs, instead of running at maximum speed by default, helps minimize power draw.

For designs with multiple subsystems, employing separate clock domains allows sections to operate only when required.

Minimize Logic Switching

Each time a logic element changes state, it consumes energy. Reducing signal transitions through careful design can lower dynamic power.

Strategies include using efficient state machines, avoiding glitches in combinational logic, and reducing fanout. Synchronous design practices also help eliminate unnecessary activity.

Implement Dynamic Voltage and Frequency Scaling

Many modern FPGAs support dynamic voltage and frequency scaling (DVFS). By lowering core voltage or reducing frequency during periods of low workload, you can save power without sacrificing overall system stability.

Monitoring workload patterns and adapting in real time ensures optimal performance per watt.

Use Power-Aware Synthesis and Placement Tools

FPGA development tools often provide power optimization features during synthesis and placement.

Enabling power-aware synthesis ensures the design is mapped and routed to minimize switching activity and resource usage.

Reviewing the power analysis reports generated by these tools can highlight hotspots and guide refinements.

Leverage Low-Power Modes

Several FPGA devices include built-in low-power or sleep modes for idle periods. Configuring the design to enter these states during inactivity can significantly reduce static power.

For example, unused logic blocks can be powered down or put into standby until needed.

Efficient I/O and Memory Management

External interfaces and memory accesses can also draw considerable power. Using low-voltage I/O standards, reducing bus widths where possible, and optimizing memory access patterns can all contribute to lower consumption.

Caching frequently used data inside the FPGA can reduce the need for high-energy external memory transactions.

Thermal Design and Cooling

Efficient power management is closely tied to effective thermal design.

Proper heat sinks, airflow planning, and board layout not only maintain safe operating temperatures but also prevent the system from consuming more power due to heat-related inefficiencies.

Continuous Monitoring and Profiling

Power management is an ongoing process. Integrating on-chip sensors and external monitoring systems allows developers to profile consumption throughout the lifecycle of the product. T

his feedback helps fine-tune designs and supports predictive maintenance in complex systems.

Conclusion

Efficient power management in FPGA projects is not limited to a single technique. It requires a combination of careful device selection, smart design practices, dynamic scaling, and continuous monitoring.

By adopting these methods early in the development process, engineers can build FPGA solutions that are not only high performing but also energy conscious, paving the way for more sustainable and cost-effective applications.

![What is FPGA Introduction to FPGA Basics [2023] computer-chip-dark-background-with-word-intel-it](https://fpgainsights.com/wp-content/uploads/2023/06/computer-chip-dark-background-with-word-intel-it-300x171.jpg)