Field Programmable Gate Arrays are foundational in modern high-performance digital systems, enabling flexible, customizable hardware solutions for aerospace, automotive, telecom, and data-intensive applications.

Unlike software development, FPGA design involves mapping logic to physical hardware, which makes simulation and testing critical to ensure reliability, performance, and functional correctness.

Errors caught late in hardware design can lead to costly re-spins, delayed deployment, or catastrophic system failures, particularly in mission-critical systems such as avionics or autonomous vehicles.

This blog provides an in-depth overview of FPGA simulation and testing tools, methodologies, verification approaches, and real-world use cases to guide senior engineers and industry practitioners in optimizing their FPGA design workflow.

Importance of Simulation and Testing in FPGA Design

FPGA designs are implemented in hardware using Hardware Description Languages (HDLs) such as VHDL and Verilog.

Unlike software, where bugs can be patched post-deployment, hardware-level errors require rework at significant cost. Simulation and testing help engineers:

- Validate logic and functionality before synthesis

- Identify timing and synchronization issues early

- Ensure adherence to protocol standards

- Optimize performance, latency, and resource usage

- Reduce debugging time on actual hardware

- Guarantee system reliability and safety in critical applications

In industries like aerospace or automotive, even minor logic errors can compromise safety or mission objectives. Therefore, robust verification practices are non-negotiable.

Key Stages of FPGA Verification

FPGA verification is a multi-layered process, combining simulation, formal verification, and hardware testing. The main stages include:

Functional Simulation

Functional simulation checks that the HDL code performs the intended operations without considering timing delays. Engineers simulate individual modules and integrated designs to verify correctness under various input scenarios. This stage is crucial for catching logical errors early.

Timing Simulation

After synthesis and placement-and-routing, timing simulation evaluates the design’s propagation delays and clock constraints. Timing violations can cause metastability or system failure in high-speed applications, making this stage critical for high-frequency FPGA designs.

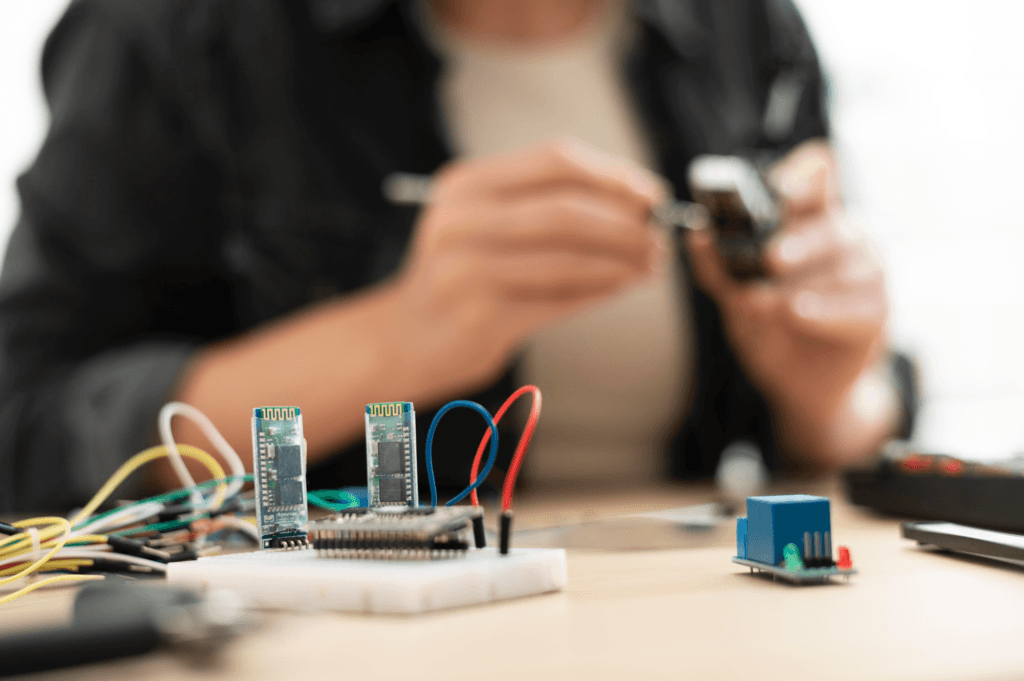

Hardware in the Loop Testing

Hardware in the Loop (HIL) testing integrates real-world hardware into the simulation environment. This approach is particularly useful for validating systems such as automotive ADAS modules, radar processing units, or aerospace navigation systems, where real input signals interact with the FPGA in real time.

Formal Verification

Formal verification uses mathematical proofs to confirm design correctness without requiring exhaustive test vectors. This technique is increasingly used in mission-critical applications such as satellite communication and high-speed trading platforms, where corner-case errors must be eliminated.

Leading FPGA Simulation Tools

Industry engineers rely on a combination of simulation tools to verify FPGA designs efficiently. Some of the most widely used tools include:

ModelSim

ModelSim is a popular simulator supporting VHDL, Verilog, and SystemVerilog. Key features include interactive debugging, waveform visualization, and scripting automation.

ModelSim is often used for small to medium-scale designs in telecom and embedded systems.

QuestaSim

An advanced version of ModelSim, QuestaSim is optimized for large-scale designs. It supports the Universal Verification Methodology (UVM), assertion-based verification, and functional coverage analysis.

QuestaSim is widely used in aerospace and automotive FPGA designs where high confidence verification is essential.

Xilinx Vivado Simulator

Integrated within the Xilinx Vivado suite, Vivado Simulator allows both behavioral and timing simulation. It offers fast compilation, built-in waveform visualization, and seamless integration with Vivado IP cores.

Aerospace and defense companies rely on Vivado for high-speed signal processing designs, including radar and avionics systems.

Intel Quartus Simulator

Native to Intel (Altera) FPGAs, this simulator provides functional and timing simulation tightly integrated with Quartus project workflows.

Telecom companies frequently use Quartus Simulator for high-speed communication protocols and 5G applications.

Aldec Riviera PRO

Riviera PRO is designed for high-performance verification of large-scale, complex designs. It supports VHDL, Verilog, and SystemVerilog with advanced debugging and automation features.

Financial and data center applications often leverage Riviera PRO for high-throughput FPGA verification.

FPGA Testing and Debugging Tools

Simulation alone is insufficient for high-confidence FPGA deployment. Hardware testing and debugging tools provide real-time visibility into internal signals and system behavior:

Vivado Integrated Logic Analyzer (ILA)

ILA allows engineers to embed a logic analyzer inside the FPGA. This enables capturing internal signals in real time, which is critical for high-speed digital designs such as aerospace navigation systems or radar processing.

Intel SignalTap II

SignalTap II is Intel’s in-system logic analyzer for FPGA designs. It captures real-time internal signals and is used extensively in automotive systems for real-time control verification.

JTAG Debuggers

JTAG interfaces enable programming, monitoring, and debugging FPGA designs directly. They are essential for low-level hardware diagnostics and are widely used across industries from industrial automation to avionics.

TestBenches

HDL-based testbenches generate input stimuli and monitor output behavior. Automated testbenches are crucial for regression testing in iterative design flows, ensuring consistent functionality across design revisions.

Hardware in the Loop Systems

HIL systems combine simulation models with real-world FPGA hardware to validate performance under operational conditions. Automotive ADAS, radar, and 5G baseband processing often use HIL verification for precise, real-time testing.

Advanced Verification Techniques

Modern FPGA verification goes beyond simulation. Advanced techniques improve confidence in complex designs:

Assertion-Based Verification (ABV)

ABV inserts logical assertions directly into the HDL code to detect violations automatically. It is commonly used in aerospace and telecom designs to ensure compliance with protocols.

Unified Verification Methodology (UVM)

UVM is a SystemVerilog-based methodology for modular, reusable verification environments. It allows standardized testbench construction and is widely adopted in complex SoC and FPGA designs.

Coverage Analysis

Coverage analysis ensures all branches, states, and conditions of a design are exercised during simulation. It provides quantifiable metrics to identify untested logic, reducing the likelihood of hidden bugs.

Formal Methods

Formal verification mathematically proves design correctness without exhaustive testing. It is particularly useful for detecting corner-case errors in safety-critical systems, such as avionics and autonomous vehicle control modules.

Real-World Use Cases

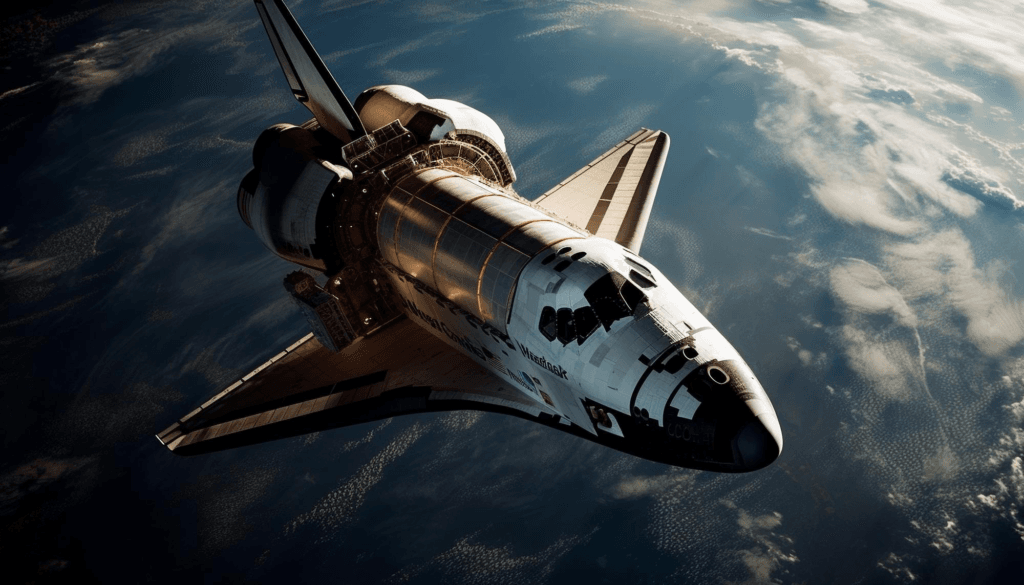

Aerospace and Defense

FPGAs are extensively used in radar signal processing, flight control systems, and satellite communications. Verification is mission-critical as design flaws can lead to catastrophic failures.

Tools like Vivado Simulator and QuestaSim, combined with HIL testing, ensure timing closure and functional correctness under extreme operational conditions.

Automotive

Autonomous vehicles rely on FPGAs for ADAS systems, sensor fusion, and high-speed vehicle control. Verification must account for multiple clock domains, real-time constraints, and functional safety standards (ISO 26262).

SignalTap II, UVM, and HIL setups are widely used to validate real-time operation.

Telecom

High-speed baseband processing for 5G networks uses FPGAs for multi-gigabit throughput. Verification involves testing JESD204B/C interfaces, PCIe Gen4/Gen5 links, and DSP pipelines.

ModelSim, Riviera PRO, and functional coverage metrics ensure robust signal processing and protocol compliance.

Data Centers

FPGAs accelerate workloads such as AI inference, encryption, and packet processing. Verification focuses on performance, latency, and reliability under extreme workloads.

QuestaSim and formal verification methods are employed to eliminate corner-case errors and ensure continuous operation.

Best Practices for FPGA Simulation and Testing

- Start verification early in the design process

- Build modular and reusable testbenches for efficiency

- Combine simulation, formal verification, and HIL testing

- Use coverage-driven verification to ensure completeness

- Automate regression tests for iterative development

- Leverage vendor-specific tools for deeper visibility

- Document test scenarios and expected outcomes for future reference

Common Challenges

- Long simulation times for complex designs

- Handling multiple clock domains and synchronization issues

- Limited visibility into internal signals on hardware

- Achieving accurate timing closure in high-speed designs

- Ensuring consistency between simulation and hardware behavior

Future Trends in FPGA Verification

- AI-assisted verification for automated test generation

- Cloud-based simulation platforms for collaborative workflows

- Virtual prototyping and digital twin integration

- Continuous integration and DevOps pipelines for FPGA development

- Increasing use of formal methods to complement traditional simulation

Conclusion

FPGA simulation and testing are the backbone of reliable, high-performance hardware design.

Combining simulation tools like ModelSim, Vivado Simulator, SignalTap, and advanced verification methodologies such as UVM and assertion-based verification allows engineers to reduce risks, optimize performance, and meet demanding industry requirements.

In aerospace, automotive, telecom, and data center applications, rigorous verification is not optional, it is the foundation for success.

By investing in comprehensive simulation and testing practices, engineers can ensure FPGA designs perform reliably in real-world environments, delivering robust and mission-critical solutions.

![What is FPGA Introduction to FPGA Basics [2023] computer-chip-dark-background-with-word-intel-it](https://fpgainsights.com/wp-content/uploads/2023/06/computer-chip-dark-background-with-word-intel-it-300x171.jpg)