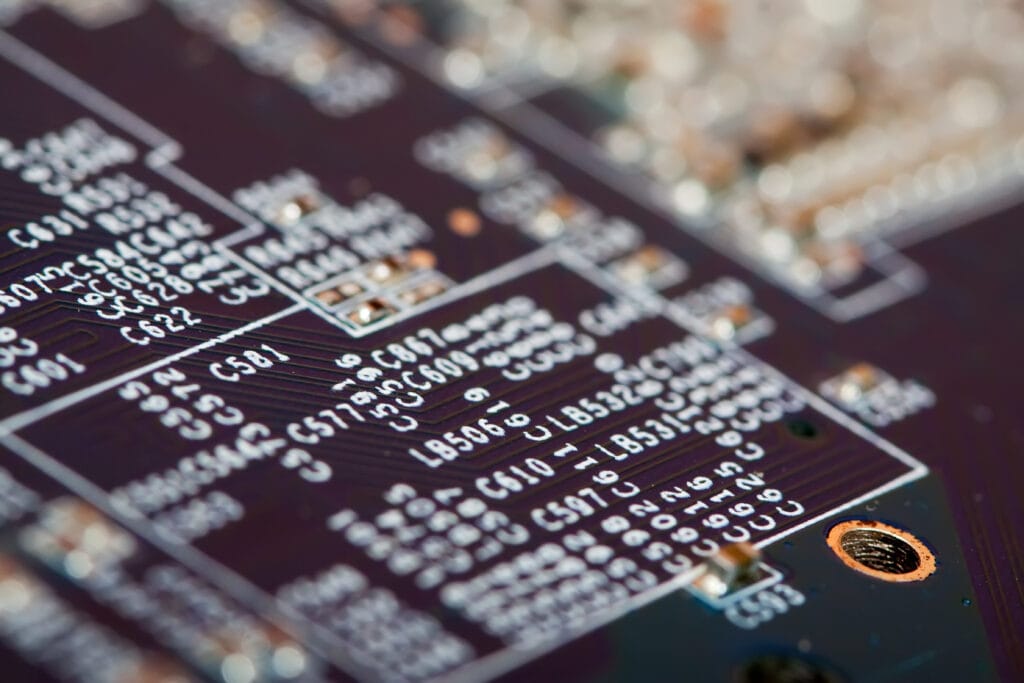

FPGAs (Field-Programmable Gate Arrays) have become a cornerstone in modern electronics, powering applications from aerospace to autonomous vehicles, AI accelerators, and high-speed communication systems.

While FPGAs offer flexibility and high performance, ensuring that the designs are robust, error-free, and reliable is crucial. This is where FPGA verification techniques play a vital role.

Understanding FPGA Verification

FPGA verification is the process of checking whether the hardware design behaves as intended before it is deployed in real-world applications.

Unlike software, hardware errors can be costly, time-consuming, and sometimes dangerous. Verification ensures the design meets specifications, functions correctly under all conditions, and avoids critical failures.

Verification can be broadly categorized into simulation-based verification, formal verification, and hardware testing.

Simulation-Based Verification

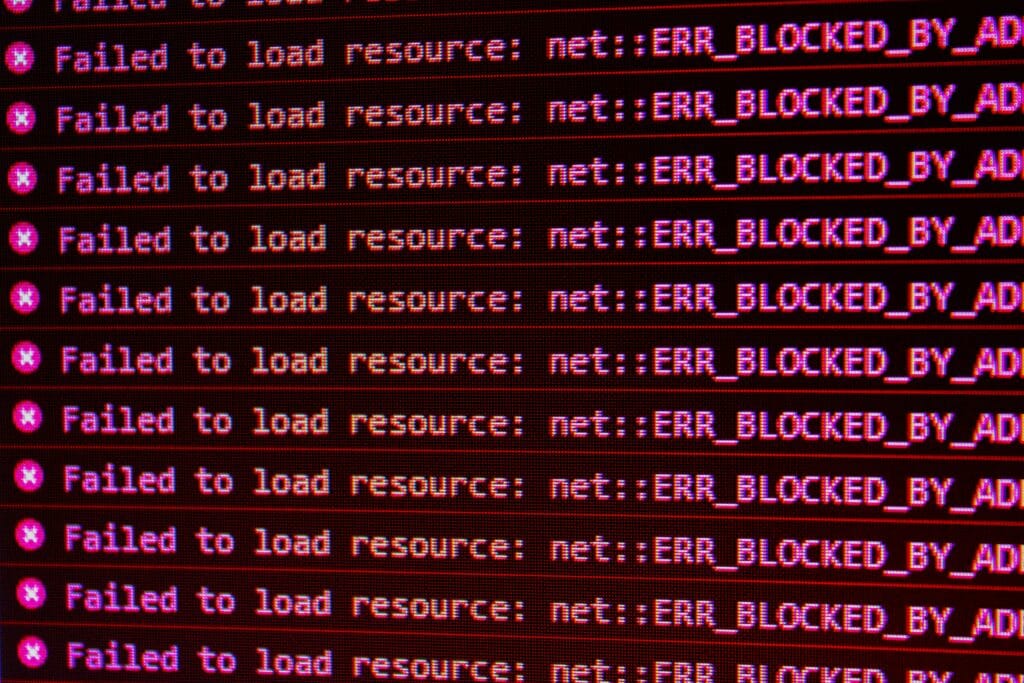

Simulation is one of the most commonly used verification techniques. It involves testing the FPGA design in a controlled, virtual environment to detect functional errors.

Key Steps in Simulation-Based Verification:

- Writing Testbenches – Testbenches simulate how the design will interact with inputs and outputs. They mimic real-world scenarios and check responses.

- Stimulus Generation – Applying different input signals to test the FPGA under various conditions.

- Monitoring Outputs – Observing the design’s behavior and comparing it with expected outcomes.

- Debugging – Identifying and fixing errors detected during simulation.

Popular tools for simulation include ModelSim, QuestaSim, Vivado Simulator, and Synopsys VCS.

Formal Verification

Formal verification is a mathematical approach used to prove that the design behaves correctly under all possible scenarios. Unlike simulation, which tests specific cases, formal verification analyzes every possible state of the design.

Benefits of Formal Verification:

- Detects corner-case errors that simulation may miss.

- Ensures compliance with design specifications.

- Reduces the risk of post-deployment failures.

Tools such as Cadence, JasperGold and Synopsys VC Formal are widely used in formal verification workflows.

Hardware Testing

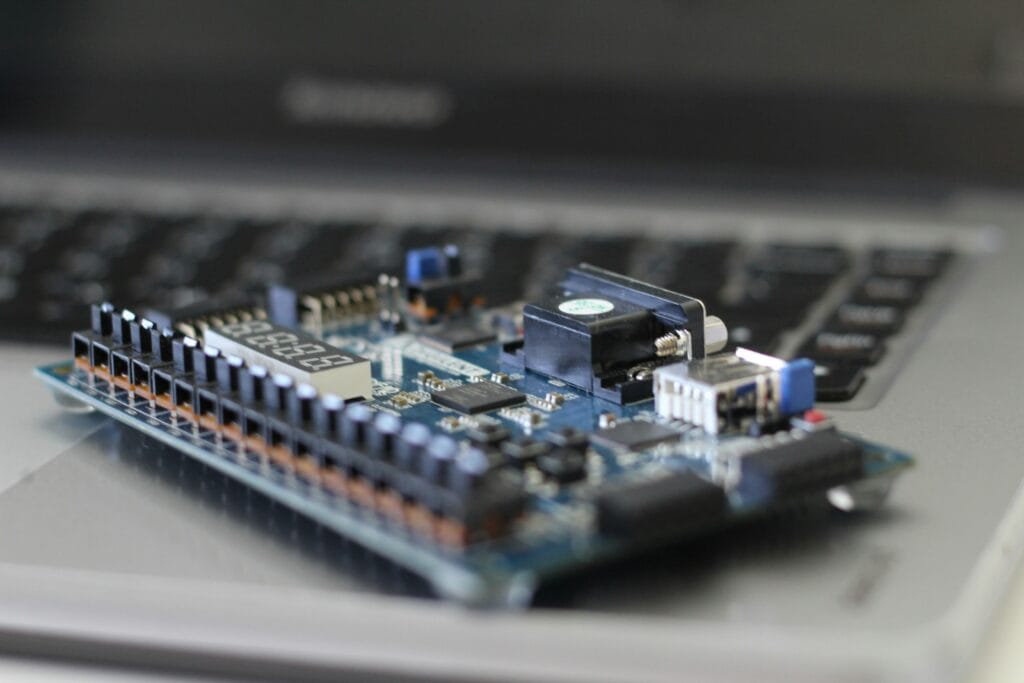

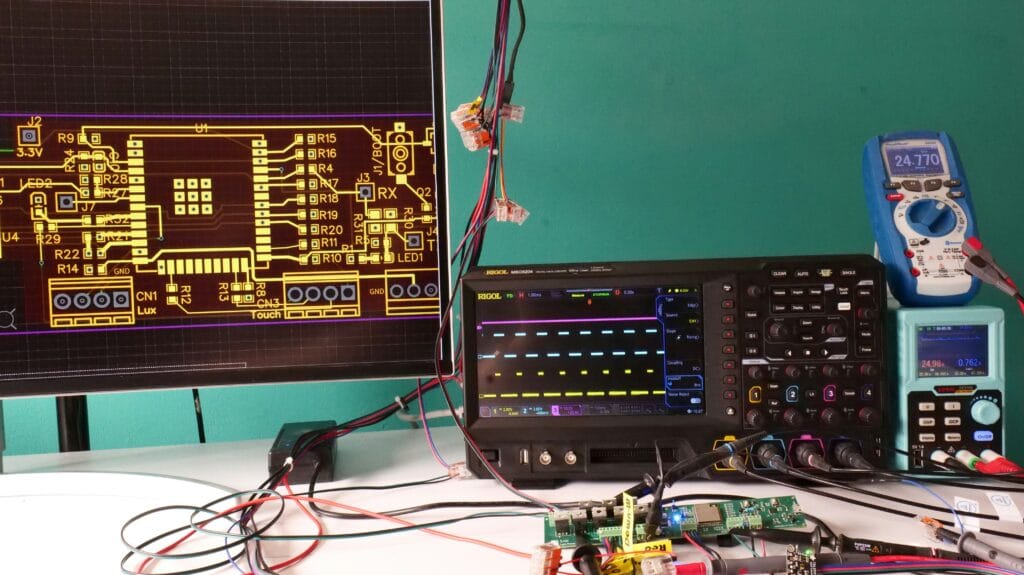

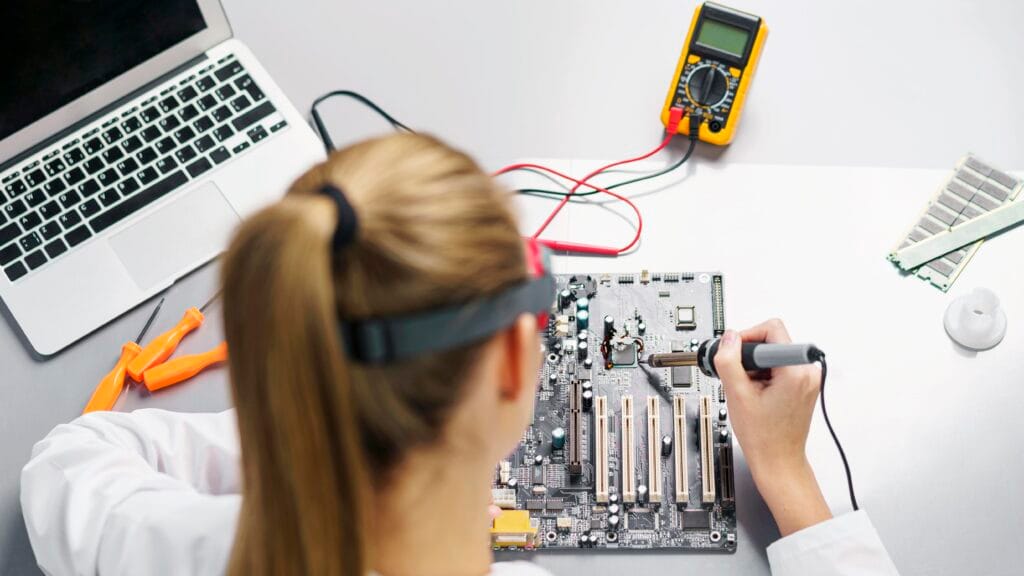

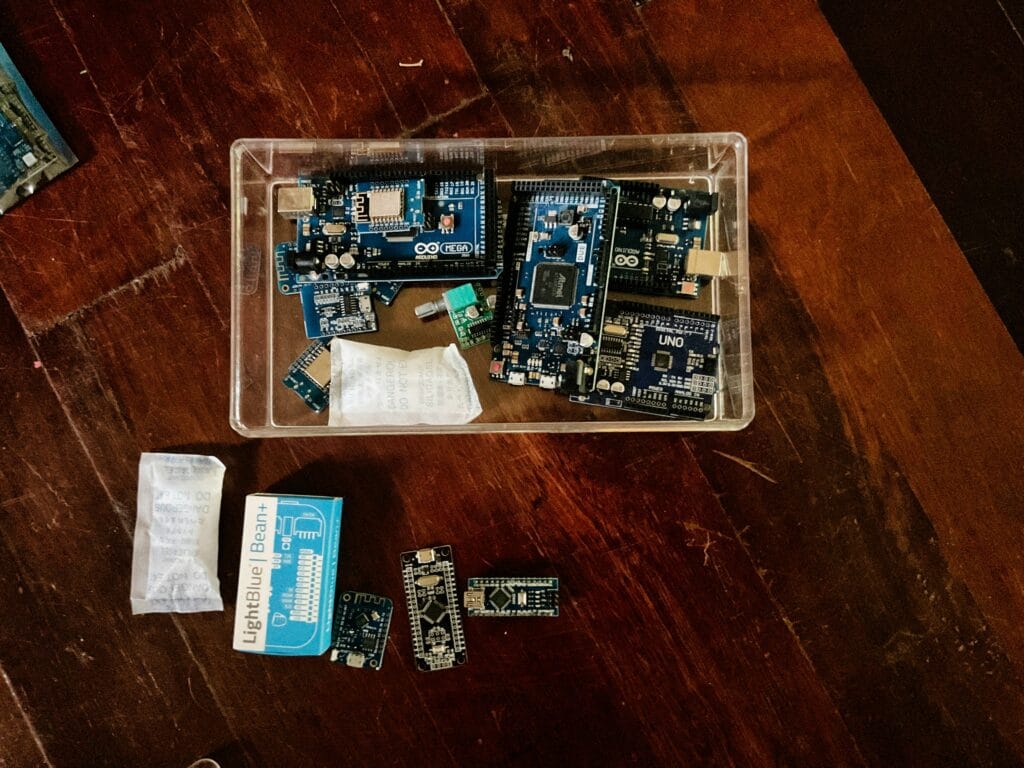

Simulation and formal verification alone cannot guarantee 100% reliability. Hardware testing involves running the FPGA design on actual hardware to validate performance in real conditions.

Hardware Testing Techniques:

- In-System Testing – Deploying the design on an FPGA development board to monitor behavior.

- Boundary Scan Testing – Checking signal integrity and connectivity at the hardware level.

- Logic Analyzer Integration – Capturing real-time signals for debugging and validation.

Hardware testing is essential for applications where timing, power consumption, and environmental factors can affect performance.

Coverage-Driven Verification

Coverage-driven verification ensures that all parts of the design are thoroughly tested. It involves defining coverage metrics to track which parts of the design have been exercised during testing.

Types of Coverage:

- Code Coverage – Ensures all lines of HDL code are executed.

- Functional Coverage – Ensures all functional scenarios are tested.

- Toggle Coverage – Ensures every signal in the design toggles between 0 and 1 at least once.

By combining coverage analysis with simulation, designers can ensure thorough validation of complex FPGA designs.

Best Practices for FPGA Verification

- Start Early – Begin verification during the design phase to detect errors early.

- Use Modular Testbenches – Build reusable testbenches for faster verification of multiple designs.

- Automate Verification – Leverage automated test frameworks for consistent and faster results.

- Perform Incremental Testing – Test small modules first before integrating the entire design.

- Combine Techniques – Use simulation, formal verification, and hardware testing together for maximum reliability.

Conclusion

FPGA verification is a critical step in delivering reliable and high-performance hardware designs. By leveraging simulation, formal methods, hardware testing, and coverage-driven approaches, engineers can identify potential issues early, ensure compliance with specifications, and deliver designs that meet the demands of modern applications.

Investing in robust verification techniques not only reduces time-to-market but also minimizes costly errors, making it an indispensable part of the FPGA development lifecycle.

![What is FPGA Introduction to FPGA Basics [2023] computer-chip-dark-background-with-word-intel-it](https://fpgainsights.com/wp-content/uploads/2023/06/computer-chip-dark-background-with-word-intel-it-300x171.jpg)