LUT in FPGA: Lookup Tables (LUTs) are essential for FPGA (Field-Programmable Gate Array) design because they make it possible to create intricate digital logic circuits.

FPGAs, which are programmable logic devices, give designers the freedom to make unique digital circuits suited to particular applications.

The idea of lookup tables, which act as the fundamental building blocks for implementing multiple logic operations within an FPGA, is crucial to this adaptability.

We will explore the construction, functioning, and applications of lookup tables in FPGA design in this blog post.

We’ll go into the implementation of Lookup Tables in FPGA systems and talk about how important they are for implementing logic functions.

We can better comprehend Lookup Tables’ function in creating complex digital systems if we have a fundamental understanding of how they work.

Understand the bigger picture of FPGA design before delving into the minutiae of Lookup Tables.

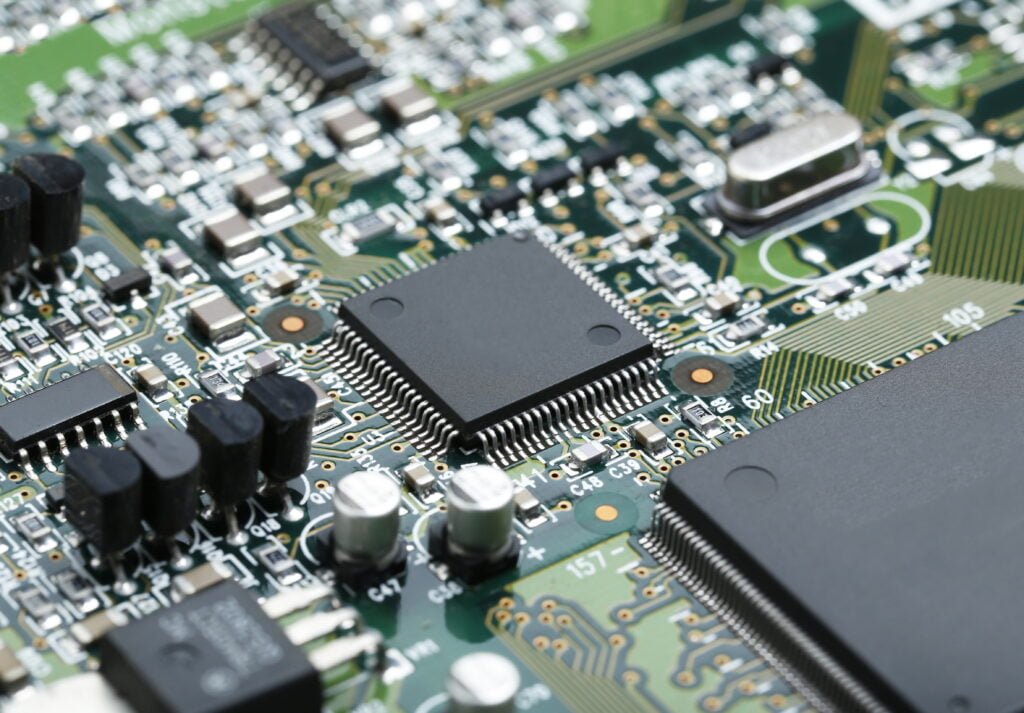

An assortment of reconfigurable logic blocks (CLBs) coupled with programmable routing resources make up FPGAs.

These CLBs include multiplexers, registers, flip-flops, lookup tables, and other functional components.

FPGAs’ flexibility to be configured by designers enables them to alter how these components are connected together and how they function in order to construct specific logic circuits.

Let’s now delve deeper into the idea of lookup tables by looking at their design and use in FPGA architectures.

What is a Lookup Table (LUT)?

A Lookup Table, as the name suggests, is an actual table that generates an output based on the inputs. Here is an example of a lookup table that implements the function of an AND gate.

Now try to picture this table being stored in tiny RAM. The address pins are inputs A and B, and the data pin is input C. Your address pins are pointing at a different address entry each time they change positions, and they are “reading out” the result, which is either 0 or 1 depending on the inputs.

According to your unique requirements and instructions, a lookup table is essentially your personalized truth table that is filled with values that are pertinent to your FPGA.

Even better, imagine your customized Lookup Table (LUT) as a tiny chunk of RAM that is loaded each time your FPGA device is turned on.

Based on your VHDL or Verilog code, it specifies and controls the behavior of the combinatorial logic of your device, referring to specified values to achieve the intended outcomes.

As a result, the inputs you supply to the Lookup Table are essentially the address lines for a RAM cell that is one bit wide.

Therefore, it makes sense that a two-input logic gate would be able to generate or accommodate four alternative combinatorial possibilities, making it appropriate for 4 x 1-bit RAM.

You can keep up with the amount of inputs you’d like to have and then adjust how much RAM you’ll need.

It follows that lookup tables essentially function as logic gates in a variety of configurations.

Use a lookup table to obtain all potential combinations rather than having to connect a variety of NAND and NOR gates.

The functionality of an FPGA chip is often broken down into a number of programmable logic blocks that are dispersed throughout the device and are each capable of operating independently while still producing coherent, unique output.

Flip flops and Lookup Tables are specific to each logic block.

These Lookup Tables determine an FPGA’s functionality and serve as the key point of differentiation across FPGA chips created for varied applications.

You should be aware that 1-bit memory cells in a table can only store one of two values: a 1 or a 0. These memory cells also have multiplexers.

As was previously said, the size of the device will primarily depend on how many inputs you need to enter into the table. LUT-Masks are the output values, and they are constructed from SRAM bits.

Following input, the device looks inside the SRAM block for the corresponding output value and outputs it at the output pin.

Implementing Logic Functions with LUT

The chip uses the Lookup Table to carry out logical functions in various combinations.

A lookup table can be used to implement any combinatorial logic operation. Since lookup tables in FPGAs provide computational range without requiring time or a high gate count, they significantly lower the costs of computation and operation.

SRAM offers configurability features for which FPGA processors are renowned, which is yet another of its many benefits when used to store data.

This means that each time the chips are powered on, the individual bits that make up SRAM can be changed and altered.

The Issue of Glitch in Lookup Tables

Although the lookup tables in the FPGA chip designs are quite useful, there is one drawback that is frequently mentioned, and that is the glitch.

When what the output is being displayed as and what it should be synchronized with, a glitch is created.

This is the result of bits in the Lookup table’s SRAM shifting and being rearranged.

Because of this, the block is unsure of what the appropriate response should be and temporarily provides an output that is erroneous.

With your use of the FPGA chip, you might not even run across this issue, but it is always a good idea to be prepared for everything.

Advantages of Lookup Tables:

- Flexibility and Configurability: Lookup tables provide a high degree of flexibility in FPGA designs. They allow designers to define complex logic functions by programming the truth table entries of the Lookup Table, enabling the implementation of a wide range of digital circuits.

- Compact representation: Lookup tables offer a compact representation of logic functions. By storing the truth table entries in memory, Lookup Tables eliminate the need for a combinatorial logic network, resulting in efficient use of FPGA resources.

- Speed and Performance: Lookup tables provide fast and predictable performance. The FPGA’s internal routing and interconnects are optimized for accessing and retrieving data from Lookup Tables, ensuring rapid execution of logic functions.

- Time-Multiplexed Operations: Lookup tables can be time-multiplexed to implement multiple logic functions or algorithms within a single Lookup Table. This approach allows designers to maximize resource utilization and optimize the overall FPGA design.

- Versatility in Implementation: Lookup Tables can be cascaded, combined, or chained together to implement more complex logic functions. This flexibility enables the implementation of arithmetic operations, data processing, and complex algorithms within an FPGA.

Disadvantages of Lookup Tables:

- Limited Resolution: Lookup tables have limited resolution, determined by the number of inputs and outputs defined in the truth table. If a logic function requires a large number of inputs or outputs, it may require multiple Lookup Tables or alternative design techniques.

- Resource Consumption: In designs with complex logic functions, the utilization of Lookup Tables can consume a significant portion of the available FPGA resources. This may lead to resource constraints and potential trade-offs with other functional elements such as memory blocks or digital signal processing (DSP) blocks.

- Propagation Delay: While Lookup Tables provide fast execution, they introduce a certain amount of propagation delay due to the time required to access the memory and retrieve the appropriate output. In designs with critical timing requirements, this delay must be considered and optimized.

- Trade-offs with Other Resources: Lookup tables compete for resources within an FPGA, such as memory blocks and DSP blocks. Designers must carefully balance the use of Lookup Tables with the requirements of other functional elements to achieve an optimal design.

- Limited Function Reusability: Lookup Tables are specific to the truth table entries defined during the design phase. Altering the logic function may require reprogramming the Lookup Table or using a different configuration altogether, limiting their reusability in certain scenarios.

Conclusion:

Lookup Tables (LUTs) are essential in FPGA design, providing flexibility, efficiency, and performance for implementing digital logic circuits.

They offer advantages such as flexibility, compact representation, fast execution, time-multiplexing, and versatility.

However, there are also limitations, including limited resolution, resource consumption, propagation delay, trade-offs with other resources, and limited function reusability.

Despite these drawbacks, Lookup Tables remain crucial for creating customized digital circuits.

By optimizing their usage and considering their advantages and limitations, FPGA designers can leverage Lookup Tables to develop innovative solutions for various applications.

![What is FPGA Introduction to FPGA Basics [2023] computer-chip-dark-background-with-word-intel-it](https://fpgainsights.com/wp-content/uploads/2023/06/computer-chip-dark-background-with-word-intel-it-300x171.jpg)