Designing with Field Programmable Gate Arrays is a powerful way to build high performance, reconfigurable systems.

Whether you are developing a data acquisition board, an AI accelerator, or a communication interface, a well structured design flow ensures efficiency and reliability.

Here is a complete guide to taking an FPGA project from the first idea to a fully deployed solution.

Define Requirements and Specifications

Begin by clarifying the purpose of the design. List the functional requirements such as processing speed, latency, number of interfaces, and expected data throughput.

Identify power budgets, operating environment, and cost constraints. Early clarity on these points saves time during implementation and helps in selecting the right FPGA family.

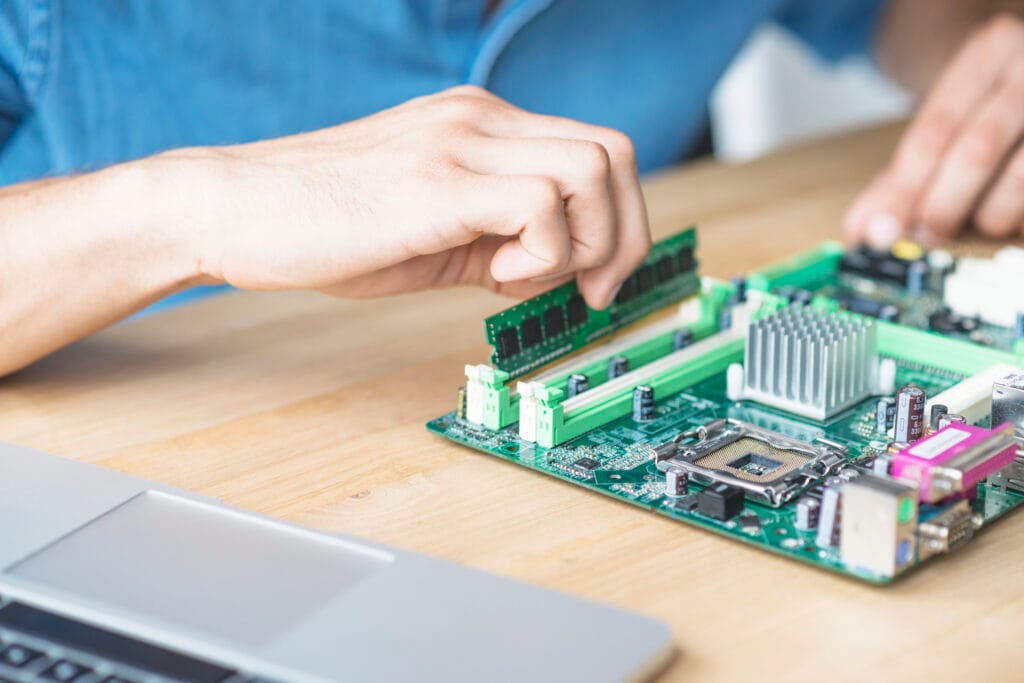

Select the Right FPGA and Development Tools

Choose an FPGA device that meets your specific design requirements, taking into account the number of logic resources, memory blocks, DSP slices, and I/O capabilities needed for your application.

Evaluate different vendors such as Xilinx, Intel (Altera), or Lattice based on factors like device availability, long-term support, performance, and cost.

Select the appropriate development toolchain and programming language for your project, typically VHDL or Verilog, but also consider high-level synthesis (HLS) if your design could benefit from using higher-level languages such as C or C++ for faster development or algorithmic exploration.

Ensuring that both the hardware and software environments align with your project goals will help streamline development and verification.

Create the System Architecture

Break down the overall design into well-defined functional modules, clearly specifying the responsibilities of each block.

Define how data will flow between these modules, how clocks and reset signals are distributed, and which external interfaces are required for communication with other systems.

Take scalability into account to allow for future updates or feature additions without major redesigns.

Creating a clear block diagram along with a detailed architecture document will provide a structured roadmap for the entire project, guiding both development and verification efforts.

Write and Simulate the HDL Code

Develop the Hardware Description Language (HDL) code for each module of your design and simulate it in the chosen development environment.

Begin with unit testing of individual components to verify their functionality in isolation, then move on to integration testing to ensure that all modules work together correctly.

Simulation allows you to identify and correct logical errors early in the design process, significantly reducing the risk of issues after hardware synthesis and saving time and resources during later stages of development.

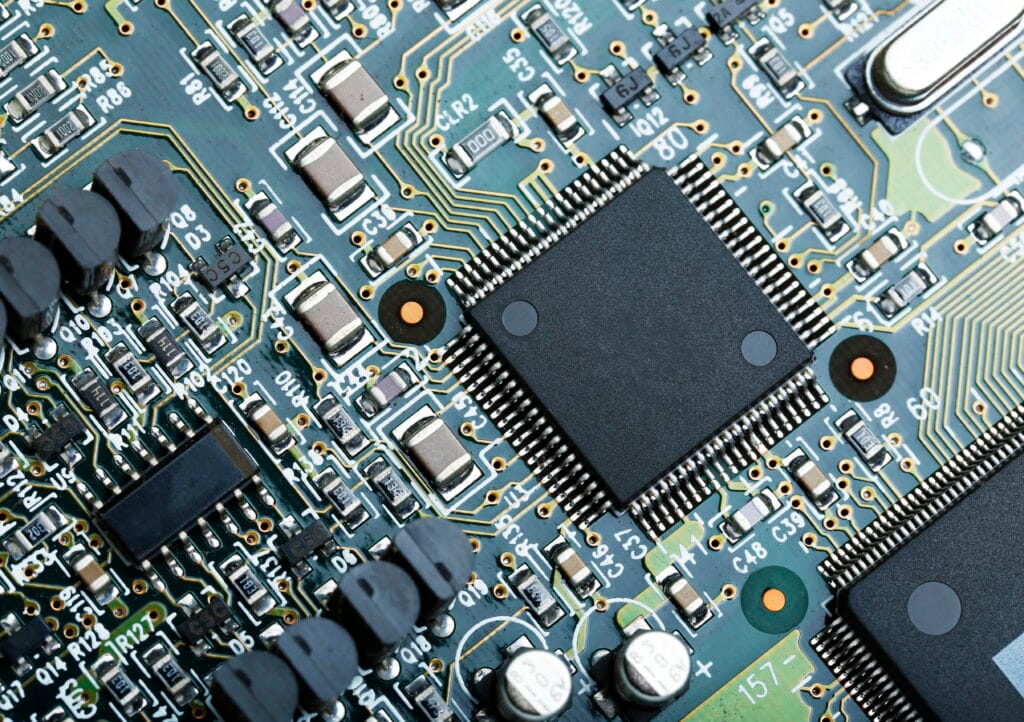

Synthesize and Implement the Design

Use the FPGA toolchain to synthesize your HDL (Hardware Description Language) code into a netlist, which represents the logical structure of your design.

Once synthesized, proceed to the implementation phase, where the design is mapped onto the physical resources of the FPGA, including look-up tables, flip-flops, DSP blocks, and I/O pins.

During this process, pay close attention to timing constraints, ensuring that critical paths meet the required setup and hold times, and monitor resource utilization to avoid overuse of FPGA elements.

Carefully review the synthesis and place-and-route reports provided by the toolchain, checking for timing violations, routing congestion, and power consumption, to confirm that the design achieves timing closure, meets performance goals, and operates efficiently within the FPGA’s capabilities.

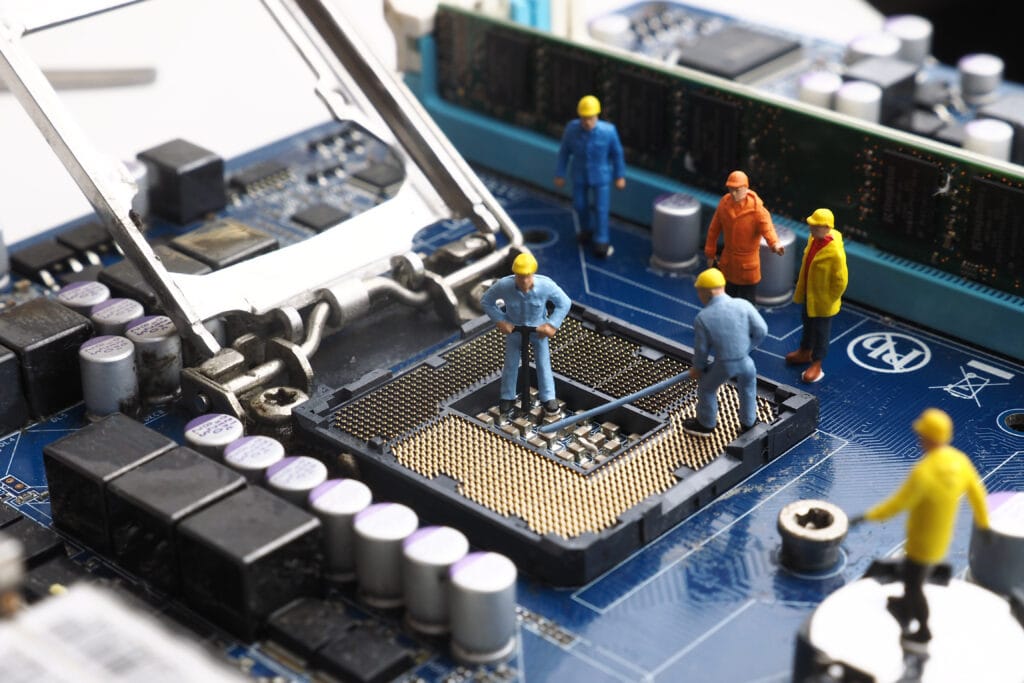

Verify on Hardware

After generating the bitstream, load it onto an evaluation board or prototype hardware to validate the design in a real-world environment.

Perform comprehensive functional testing using actual input signals, and stress the design under a wide range of operating conditions to ensure stability and robustness.

To gain deeper visibility into the system, use instrumentation tools such as logic analyzers, oscilloscopes, and embedded logic probes, which allow observation of internal signals and detection of hidden timing or functional issues.

This stage is critical for uncovering edge cases that may not appear during simulation, ensuring the FPGA design is truly deployment-ready.

Optimize for Performance and Power

After initial testing, the design should be refined for speed, area, and overall energy efficiency.

Engineers can apply techniques such as pipelining, retiming, and resource sharing to balance performance and resource usage.

Additionally, optimizing clock domains and reducing unnecessary switching activity are crucial steps to minimize dynamic power consumption and enhance reliability.

Plan for Deployment and Maintenance

Once the design meets all required specifications, the next step is to generate production-ready bitstreams and thoroughly document the entire design process.

Proper documentation ensures that the design can be easily maintained, debugged, or handed off to other teams.

It is equally important to establish a clear version control system along with an update strategy to manage field upgrades, bug fixes, and performance improvements.

To future-proof the project, designers should also consider how evolving requirements could be supported through techniques like partial reconfiguration, modular design, or scalable architectures, enabling seamless enhancements without a full redesign.

Final Thoughts

A structured FPGA design flow transforms an initial concept into a robust, deployable system.

By carefully defining requirements, choosing the right hardware, simulating thoroughly, and testing on real hardware, you can achieve a design that meets performance goals and is maintainable over the product’s lifetime.

This systematic approach ensures your FPGA project moves smoothly from idea to implementation and remains reliable in the field.

![What is FPGA Introduction to FPGA Basics [2023] computer-chip-dark-background-with-word-intel-it](https://fpgainsights.com/wp-content/uploads/2023/06/computer-chip-dark-background-with-word-intel-it-300x171.jpg)