This article explores PCIe 6.0 in-depth, providing a detailed analysis of what it is, its important characteristics, and how it has the potential to change the computing landscape.

Faster data transfer and communication between hardware components are essential in the constantly evolving world of computer technology. Peripheral Component Interconnect Express (PCIe), which has been at the vanguard of this growth, has recently released PCIe 6.0, which represents yet another significant improvement in data transfer rates and capabilities.

What is PCIe 6.0?

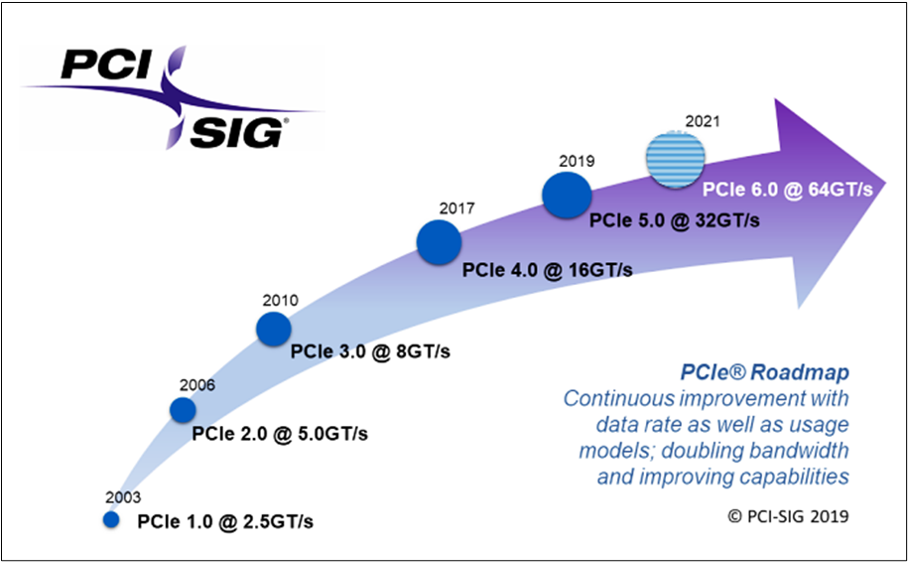

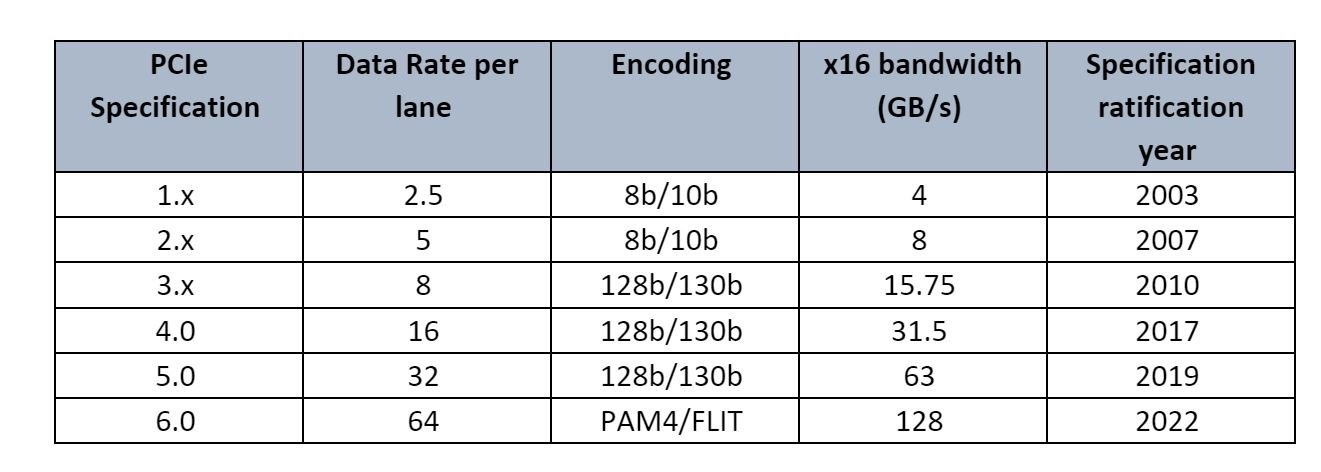

The common interface for high-speed component connections to the CPU is called Peripheral Component Interconnect Express (PCIe). The PCIe standard, which the PCI Special Interest Group (PCI-SIG) first proposed in 2003, is now in its sixth successful generation. In order to support new compute-intensive applications like artificial intelligence (AI) and machine learning (ML), PCIe 6.0 introduces a number of new features and capabilities.

PCIe Gen6 doubles the data rate while maintaining backward compatibility with earlier generations, much like all prior updates. In addition to offering enough capacity for next-generation GPUs, ultra-fast non-volatile memory express (NVMe), and Compute Express Link (CXL) solutions, PCIe 6.0 bandwidth allows the switch to 800G Ethernet for cloud computing workloads. The bandwidth-doubling tradition required major modulation (PAM4) and error correction (FEC) upgrades for the first time.

Why do we need PCIe 6.0?

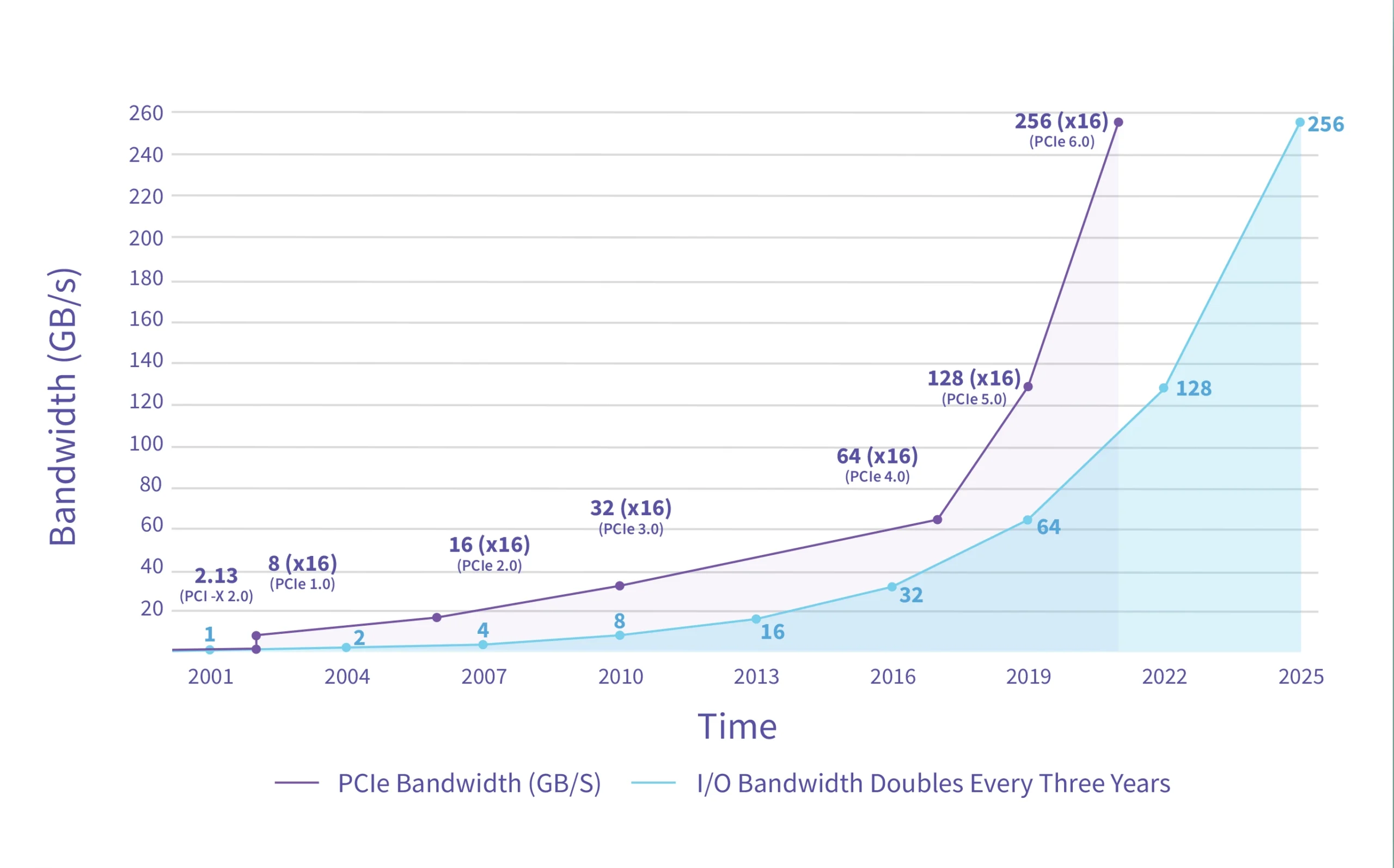

In terms of the available bandwidth needed for use cases prior to 2015, PCIe was far ahead of the competition. Because there was no business incentive to run faster, the specification evolved more slowly. Global data traffic has skyrocketed since 2015. As data centers switched to 100G Ethernet (and higher), PCIe interconnects in servers and networking equipment became the bottleneck.

The switch to 800G Ethernet in data centers is completely supported by the PCIe 6.0 specification: The bandwidth needed for 800 gigabits per second (Gb/s) is 100 GB/s, falling inside the 128 GB/s limit of an x16 PCIe 6.0 link. 800G Ethernet, like PCIe, is a full duplex. Furthermore, PCIe 6.0 is not just driven by networking and general computing in data centers. Accelerators for AI and machine learning constantly crave greater bandwidth. Speed is crucial for processing AI/ML training models, and the more quickly accelerators can transfer data in and out, the more effectively and affordably the training can be carried out.

How Does PCIe 6.0 Improve on PCIe 5.0?

Important updates were made to the PCIe protocol to provide increased speed and lower latency:

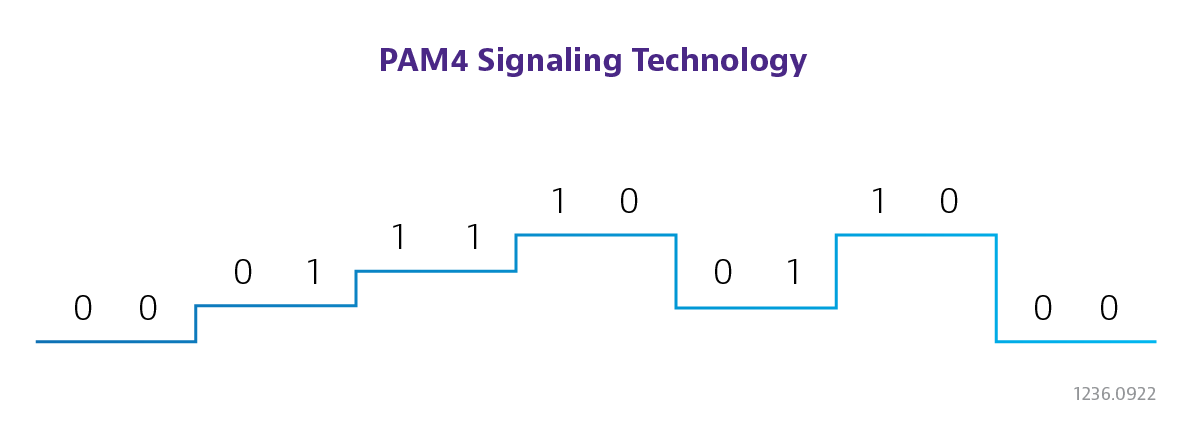

PAM4 Modulation

PAM4 modulation doubles the bandwidth of binary non-return-to-zero (NRZ) modulation by employing four amplitude pulses, each containing two bits, to facilitate high-speed data transmission. Data rates of 64 GT/s are now attainable while lowering channel loss and expanding reach thanks to the introduction of PAM4.

Forward Error Correction (FEC)

Tightly spaced voltage levels decrease the signal-to-noise ratio (SNR) and raise the bit-error rate, even though PAM4 is essential to PCIe Gen 6’s increased throughput. This trade-off in performance is made up for by forward error correction (FEC). Additional FEC latency is restricted by the PCIe 6.0 specification to two nanoseconds or less. To keep the link retry chance low, FEC and CRC (cycle redundancy checks) work together.

FLIT Mode:

The addition of FEC is now a plus rather than a drawback thanks to FLIT Mode. To support the fixed packet size requirements of FEC, PCIe 6.0 included encoding based on flow control units (FLIT). By doing away with the necessity of framing packets at the physical layer, this modification also streamlined data management procedures decreased latency, and increased efficiency.

The Impact of PAM4 Signaling

It was important that PCIe Gen 6 added pulse amplitude modulation with four levels (PAM4). To improve PCIe 6.0 performance and support upcoming technological markets, PCI-SIG determined that an upgrade was required. Since its inclusion in the IEEE 802.3 Ethernet standard in 2017, PAM4 signaling has expanded throughout high-speed network components.

PAM4 vs NRZ: For all prior generations of PCIe, simple non-return-to-zero signaling with simply two signal levels (1 or 0) that represented digital information through a positive or negative voltage was adequate. By using four discrete signal levels (0, 1, 2, and 3), each of which carries two bits of logic, PAM4 offers increased bandwidth.

Signal Analysis: Due to increased levels of signal noise, distortion, and dispersion, the inclusion of PAM4 creates significant technical hurdles. In order to evaluate signal integrity and lane margining in terms of voltage and time margining, PAM4 uses three-eye diagrams. Signal deterioration problems are reduced with the aid of distortion and adaptive equalization techniques.

Interoperability: Interoperability issues were also brought on by the switch from the 128b/130b encoding technique that has been in use since PCIe 3.0 to PAM4/FLIT encoding. PCI-SIG added additional circuitry and logic to cohabit with the old NRZ circuitry and logic in order to remedy this problem. To avoid allocating separate pins and slots for each mode, this increased expense was a required trade-off.

PCIe 6.0 encoding

Every 8 bits of data were converted into 10-bit characters before being delivered in PCIe versions 1.0 and 2.0, which results in a 20% overhead (you must transfer 10 bits of data even though you’re only attempting to send 8). To communicate those same 2 extra bits, PCIe 3.0, 4.0, and 5.0 all employ 128b/130b encoding, which reduces the overhead to just 1.5%.

The data encoded has minimal overhead because PCIe 6.0 uses 1-bit to 1-bit (1b/1b) encoding, according to the PCI-SIG. This means that you just need to send 8 bits if you want to send 8 bits across PCIe gen 6. The overhead still exists in the form of extra FEC/CRC packets, though.

PCIe 6.0 Enhancements

When discussing the PCI Express base standard revision 6.0, PAM4 and FEC receive the majority of the focus. These well-known features increased efficiency and effectiveness while complicating the testing procedures for protocol analysis, error detection, jamming, and trace analysis. The PCIe6 specification also includes the following upgrades:

Cyclic Redundant Check (CRC): Cyclic redundancy check error detection was included in addition to FEC. CRC coding detects errors, whereas FEC corrects problems at the receiver by delivering new data. The “lightweight” version of PCIe 6.0 FEC was made possible by this secondary error-correcting mode, which also reduced latency.

New L0p Power State: Power-saving design improvements were given top attention because PAM4 signaling consumes more energy. Similar to a light switch’s dimmer, the new low power state known as L0p enables bandwidth scaling up or down without halting data flow. Compared to PCIe 5.0, this has led to increased power efficiency.

Component Measurement and Authentication (CMA): The PCIe 6.0 specification gave top importance to security features. Each PCIe device has a cryptographic signature produced by CMA using firmware. To identify or prevent security risks, engineers and IT teams check the accuracy of signatures. Another new security feature that shields PCIe 6.0 FLIT packets from hacker attempts is integrity and data encryption (IDE).

PCIe 6.0 Specification Features

- 64 GT/s raw data throughput and x16 configuration for up to 256 GB/s

- PAM4 signaling, which uses the already-existing PAM4 technology that is now accessible in the market

- PAM4 signaling causes an increase in bit error rates, however lightweight forward error correction (FEC) and cyclic redundancy check (CRC) reduce that increase.

- PAM4 modulation is supported by Flit (flow control unit) based encoding, which also utilizes the FEC and CRC to quadruple bandwidth gain.

- Flit Mode’s updated packet architecture provides more functionality and streamlines processing.

- Maintains compatibility with all prior PCIe technology generations

PCIe Gen 6 Speeds Enable Advanced Applications

Despite the design and efficiency upgrades, PCIe Gen 6 speed continues to be of interest to the general public and industry. The performance of PCIe 6.0 has increased significantly thanks to the extension of the double-doubling custom. This has improved performance for current use cases while opening up new possibilities for the PCIe interface.

In order to create a shared memory pool for attached devices, Compute Express Link (CXL) took advantage of the PCIe 5.0 feature that enabled support for alternative protocols. PCIe5 speeds were used in the initial deployment of CXL implementations. With PCIe6, CXL applications are anticipated to grow much further.

Eight lanes and 100 GB/sec of bandwidth are needed for 800G Ethernet. Due to the rapid transition from 400G to 800G for high-density switches and other bandwidth-hungry applications, hyperscale data centers. A x16 PCI Express 6.0 link with a 128 GB/sec bandwidth is required due to the rapid expansion of data centers.

Industry 4.0, driverless vehicles, and the Internet of Things (IoT) are a few examples of data-intensive applications that will keep growing as new 5G networks are introduced. The demands of these new use cases are supported by PCIe 6.0’s 64 GT/sec data throughput and low latency.

With rising bandwidth and latency demands, military and aerospace applications have continuously benefited from PCIe high-speed data transfer for sophisticated satellite communication, high-resolution sensors, and onboard data processing systems. PCIe 6.0 speed doubling supports these businesses’ ongoing adoption of new technology.

The PCIe 6.0 requirements have been adopted early by hyperscale data centers. The hyperscale industry is prepared to adopt PCIe Gen 6 speed to maintain performance, scalability, and efficiency goals, even though consumer goods may be a generation or more behind. Hyperscale storage capacity restrictions are lessened by PCIe 6.0 SSDs that use stacked die technology.

PCIe 6.0 technology is used by artificial intelligence (AI) and machine learning (ML) for high bandwidth GPU and AI accelerator interfaces. PCIe Gen 6 offers the incredibly quick transfer rates needed for ML training cycles across numerous processors. The needs of AI engines can be met by disaggregated high-performance computing (HPC) in hyperscale data centers.

By using multi-state qubits instead of conventional computing bits, quantum computing has the potential to redefine processing speeds. Even if quantum computing is still in its infancy, exponentially faster processing is of little use without PCIe 6.0’s fast data transport and error correction features.

Is PCIe 6.0 backward compatible?

PCIe 6.0 is backward compatible with all earlier PCIe generations, just like all PCIe versions are. It’s crucial to remember that the slower generation will only be able to transport data at a restricted speed. For instance, a PCIe 5.0 SSD will only operate at PCIe 5.0 speeds when connected to a Gen 6 slot. The opposite is also true; a PCIe 6.0 SSD will transport data at Gen 5 speeds when plugged into a Gen 5 slot.

PCI 6.0 and Beyond

The three-year development cycle that featured substantial architectural hurdles and advancements resulted in the release of PCIe 6.0 in January 2022. The designers of PCIe Gen 6 upheld standards for new PCIe releases and raised the bar for following generations by keeping backward compatibility while further tripling speed.

The PCI-SIG highlighted the sophisticated uses for PCIe 6.0 technology that have already transcended the constraints of PCIe 5.0 connections and SSDs as part of the formal PCIe Gen 6 spec announcement.

With the release of PCIe 7.0 anticipated for 2025, PCI-SIG is anticipated to retain its three-year release cadence for the foreseeable future. PAM4 modulation and FEC will remain in place, along with 512 GB/sec of bi-directional throughput across a 16-lane link.

The most recent developments in HPC, AI/ML, and quantum computing will reach the next performance plateau with additional design improvements to increase efficiency and reach. The secret to continuing this wave of development will be PCIe test and troubleshooting procedures.

Conclusion

In conclusion, PCIe 6.0 represents a significant advancement in data transport technology and computer hardware. It has the potential to completely transform a number of industries, from gaming and entertainment to data centers and scientific computing, thanks to its amazing data speeds, increased efficiency, and expanded capabilities. The need for quicker and more effective data transfer will only increase as the digital era progresses, and PCIe 6.0 is well-positioned to meet these needs head-on.

The incorporation of energy savings and backward compatibility with prior PCIe versions in PCIe 6.0 provides a seamless transition for both consumers and manufacturers. PCIe 6.0’s future appears bright, and while it might take some time for it to become widely used in the computing industry, it will surely play a significant role in determining the next generation of high-performance computing systems. Therefore, keep a watch on PCIe 6.0 as it continues to revolutionize how we connect and communicate online.

Explore Frequently Asked Questions here:

1) What is PCIe 6.0 flit mode?

The Flow Control Unit (FLIT) encoding employed by the PCIe 6.0 specification allows for maximum efficiency and minimal latency. Due to the requirement that error correction function on fixed-sized packets, FLIT is used in the PCIe 6.0 design.

2) What is the latency of PCIe Gen 6?

Tightly spaced voltage levels reduce the signal-to-noise ratio (SNR) and raise the bit-error rate, despite the fact that PAM4 is essential for PCIe Gen 6’s increased throughput. For this performance trade-off, Forward Error Correction (FEC) makes up for it. The PCIe 6.0 specification caps additional FEC delay at two nanoseconds or less.

3) How big is the PCIe 6 FLIT?

256-Byte

PCIe 6.0 has adopted 256-byte FLITs as the default size of the data transfer unit because FEC can only operate on fixed-sized data packets.

4) What is PCIe 6.0 used for?

The connectivity solution for data-intensive applications including Data Centers, AI/ML, HPC, Automotive, IoT, and Military/Aerospace is PCIe 6.0 technology, which is both affordable and scalable.

5) What are the features of PCIe Gen 6?

The data throughput is increased by PCIe 6.0 to 64 Giga transfers per second (GT/s), which is twice as fast as PCIe 5.0. The link’s bandwidth can reach 128 gigabytes per second (GB/s) for an x16 link, which is typical of graphics and network devices.

6) What is the maximum speed of PCIe 6?

The complete specifications for PCIe 6.0 have been released by the PCI Special Interest Group, which doubles the bandwidth over PCIe 5.0 to a theoretical maximum bidirectional speed of 256GBps on an x16 slot (128GBps in one direction).

7) What are PCIe 6 2-pin connectors?

A 6+2-pin connector is technically an 8-pin connector, but since it is broken into two halves, you may also use it as a 6-pin power line if necessary.

8) What are PCIe 6-pin connectors for?

Low- and mid-end graphics cards often have 6-pin power connections. The 6-pin power connector, which completely avoids the motherboard, has a 4.2mm pitch and can draw up to 75 watts of power from an external power source.

Note: This post is sponsored from our active user. Get your post published, Contact us now.